Alright, let’s cut through the noise. Nobody wants to talk about how much of a dumpster fire quantum error correction is right now, especially if you’re actually trying to *do* something with these machines beyond academic papers. We’re talking about a different game, one where understanding the *actual* noise profile of a backend is the key. Those esoteric concepts of **topological quantum error correction** might just be the secret sauce, for unlocking what’s possible right now.

Inspired by Topological Quantum Error Correction

This isn’t about building the next theoretical marvel. It’s about getting your hands dirty with the hardware you have *today* and proving out use cases. Consider the ideal of **topological quantum error correction**– with its inherent robustness against local errors through encoded logical qubits – paints a picture of a future where noise is a minor inconvenience. But what if we borrow from that *idea* of robustness, not the implementation?

Embedding Gates in Symmetric Motifs for Enhanced Fidelity

Hypothesize that strategically embedding gate operations within recursively symmetric circuit motifs, inspired by the error-resistance principles of **topological quantum error correction** but mapped to physical connectivity and calibration data, will yield a demonstrably higher fidelity for specific computational tasks (e.g., modular arithmetic subroutines within ECDLP algorithms) compared to flat circuit implementations, *even when accounting for similar levels of overall qubit decoherence*.

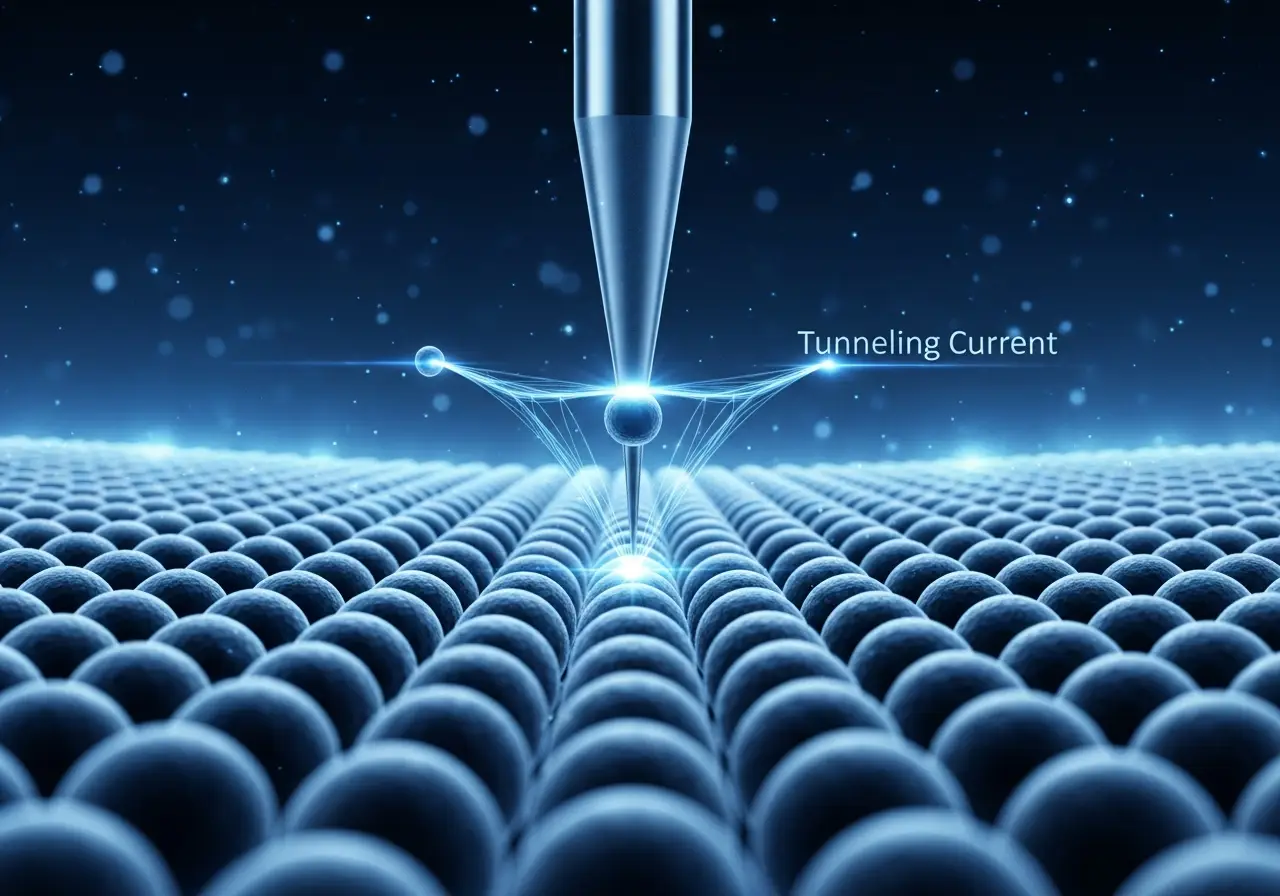

Topological Motifs and V5 Measurement for Enhanced ECDLP Benchmarking

Specifically, test the following: 1. Fingerprint the Backend. 2. Design Recursive Motifs. 3. Implement V5 Measurement Discipline. 4. Benchmark ECDLP. The expectation is that the circuit designed with the spirit of **topological quantum error correction** in mind, combined with rigorous V5 measurement exclusion, will outperform the flat design on the same hardware. It’s about making noise work *for* you, by understanding its patterns.

Topological Quantum Error Correction Principles in NISQ Advantage

This isn’t magic. It’s pragmatic engineering on a quantum substrate. The 3-5 year risk timeline for CISOs is not about waiting for fault tolerance; it’s about understanding how to extract advantage from NISQ *today*. The question isn’t *if* you can solve problems; it’s *how* you’re going to account for the hardware you have.

For More Check Out